| |

Industry's most advanced and scalable multi-user

verification planning and management solution

Key Benefits

• Accelerates data collection, management, and analysis of functional verification, with

15X greater scalability than file-based tools

• Automates verification signoff utilizing executable verification plans, while reducing

farm utilization by 25%

• Improves design quality using forward-looking metrics and the Metric-Driven Verification

methodology for up to 60% reduction in total verification time

The Cadence® vManager™

Metric-Driven Signoff Platform is

a first-of-its-kind automation

platform for verification planning

and management. The vManager

platform is a true enterprise-class

solution fueled by client-server

technology, a commercial SQL

database, and an industry-

standard enterprise API, all of

which mean scalability for small

to ultra-large verification projects.

|

|

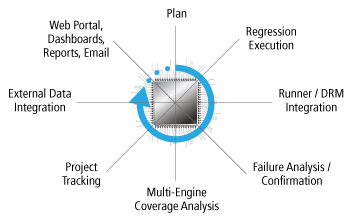

| Comprehensive and Integrated vManager Platform |

The heart of the functional verification process is the verification plan (vPlan), which back-annotates results

to a live plan (executable), and defines verification complete. With the vManager platform, you can improve

your design quality while benefiting from improved productivity, predictability, controllability, and coordination

of your functional verification process. The vManager platform can execute pre-silicon verification testing with

Cadence’s Xcelium® Parallel Simulator, JasperGold® Formal Verification Platform, or Palladium Z1® Enterprise

Emulation Platform.

The vManager platform can be used to manage the following verification initiatives:

• Formal designer handoff – Utilize assertions, directed scenarios, and formal verification “apps” to

get to designer verification faster and easier than simulation, with clear handoff guidelines to the

verification team

• RTL digital simulation or acceleration – Verify digital designs from IP to SoC at RTL or gate level,

with a comprehensive set of coverage metrics compatible across the Cadence Verification Suite,

optimized by the JasperGold platform, and accelerated by the Palladium Z1 platform

• Mixed-signal verification – Real number modeling verification and integration with the Cadence

Virtuoso® ADE Verifier accelerates closure of analog or mixed signal designs and provides optimal

R&D efficiency

• Low-power verification– Verify all power domains, power-up sequences, and user-driven scenarios

starting with CPF or IEEE 1801 definition files, which are visible as verification plans with back-annotated

results driven by the vManager platform

• Functional safety verification – Leveraging the same functional verification environment, define

failure modes, formally reduce fault space, and automatically execute fault campaigns with traceability

to verification and safety

• Software-driven verification – Combine IP from many sources, assemble, and execute integration

test scenarios using the Cadence Perspec™ System Verifier’s pre-defined libraries or user-written

libraries, changing the focus from RTL metrics to exhaustive use-case coverage and integration

verification

• HLS verification – Starting with a high-level design in C/C++ and Stratus™ High-Level Synthesis

(HLS), shift left your functional verification efforts to spend less time verifying the model and less time

verifying the synthesized RT

• Application software verification – Define application software test scenarios, execute jobs to the

Cadence Protium™ S1 Rapid-Prototyping Platform, and measure test results and software code coverage

metrics

For RTL designers

The vManager platform lets you easily define and execute your own tests or tests written for you from the

verification engineer, and collaborate with your verification team in real time, sharing test cases and doing

route cause analysis. Tests can be based on the Xcelium simulator or the JasperGold platform, using the

vManager platform to share results.

For functional verification engineers

The vManager platform is the ultimate experience to directly measure functional progress and drill down

to bin-level details of the unified coverage database (UNICOV) with the embedded Integrated Metrics Center

(IMC). The vManager platform can optimize the farm with ranked tests and smart regressions. Post-execution,

the vManager platform will aggregate and merge coverage across engines to see a single result, and intuitively

organize verification plans by features to maximize comprehension and reporting visibility.

For functional safety engineers

A single cockpit provides execution to results starting from FMEDA plans, to optimization techniques using

formal engines, fault campaign execution of hundreds to thousands of faults in parallel, and traceability

and reporting per ISO 26262 guidelines.

For design verification and project managers

The vManager platform provides the automation for aggregating and reporting results, based on real project

metrics. Enabled by data congruency across the Cadence Verification Suite, the vManager platform tracks

projects and subprojects individually, and aggregates results to a single unified view. It tracks progress,

compares to goals, and provides a simplified web-based dashboard for easy viewing and measurement of

milestones.

Key Features

The vManager platform is a true enterprise-class infrastructure that:

• Supports multiple users and user types simultaneously

• Enables configuration of multiple projects using a single infrastructure

• Provides deep integration to execute on a Xcelium, JasperGold, Palladium Z1, or Protium S1 platform

• Aggregates data across multiple sites and enables remote access for remote engineers

|