| |

First production-proven parallel simulator with multi-core computing technology

Key Benefits

• Provides an average 2X improved single-core performance

• Offers an average multi-core performance speed-up of 3X for RTL design simulation,

5X for GLS, and 10X for DFT simulations running on today’s servers

• Provides parallelism with multi-core speed-up, benefiting event-dense simulation runs

of all types

• Further extends innovation within the Cadence Verification Suite

The Cadence® Xcelium™ Parallel Simulator is the EDA industry’s first production-ready third-generation

simulator. It is based on innovative multi-core parallel computing technology, enabling systems-on-chip

(SoCs) to get to market faster than current solutions. On average, customers can achieve 2X improved

single-core performance and more than 5X improved multi-core performance versus previous generation

simulators. The Xcelium simulator is production proven, having been deployed to early adopters across

mobile, graphics, server, consumer, IoT, and automotive projects.

The Xcelium simulator offers the following benefits aimed at accelerating system development:

Multi-core engine architected for fast SoC simulation

• Patented solution automatically analyzes design and selects optimal configuration for speed

• Provides an average speed-up of 3X for register-transfer level (RTL), 5X for gate-level simulation (GLS),

and 10X for design for test (DFT)

Single-core engine refactored for fast IP simulation

• Proven engine runs comprehensive set of simulation use cases

• Provides an average of 2X speed-up over the Cadence Incisive® Enterprise Simulator

Productivity features enable efficient verification

• Innovative solutions on top of fast engines reduce overall project time

• Provides enhanced smart exclusion flow and parallel multi-core

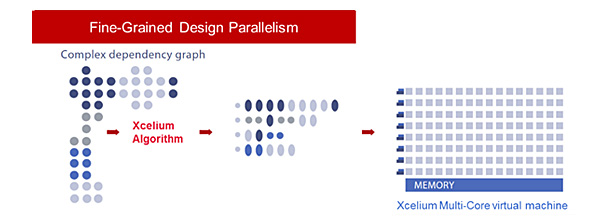

The multi-core engine in the Xcelium simulator provides fine-grained design parallelism to speed-up SoC

simulations that run for days or weeks in second-generation simulators.

Its unique compile/elaboration process analyzes each design's dependency graph and automatically maps

it to the optimal number of cores to maximize its speed. Users can set the number of cores on the command

line without recompile. The Xcelium Parallel Simulator further extends innovation within the Cadence

Verification Suite, which is comprised of best-in-class core engines, verification fabric technologies, and

solutions that increase design quality and throughput, thus fulfilling verification requirements for a wide

variety of use cases and vertical segments.

|