| |

Run full bus simulations in hours instead of days

Key Benefits

• Lets you run full bus simulations in hours instead of days

• Retains transistor-level accuracy

• Generates IBIS 6.0 power-aware models

• Part of a globally supported SI/PI product family

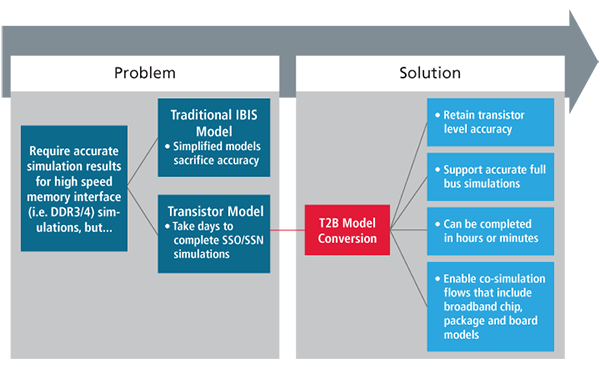

To keep up with the rapid advances in high-speed interfaces, you need to be able to

run accurate, full-bus simulations in hours, instead of days. By converting models

from transistor to power-aware IBIS behavioral, Cadence® Sigrity™

Transistor-to-Behavioral Model Conversion (T2B™) can help you meet ever-shorter

deadlines by avoiding time-consuming transistor-level simulation and inaccurate

non-power-aware IBIS model simulation.

Along with saving you time, the Sigrity T2B solution preserves co-simulation flows that

include broadband chip, package and flow models, by giving you output models in IBIS

3.2, 4.2, 5.0, and 6.0 formats, as well as in an accuracy-enhanced Sigrity behavioral

model format. Also, the power-aware behavioral driver models generated by the Sigrity

T2B solution further ensure accuracy and support highly efficient simulations using Sigrity

SPEED 2000™ and Sigrity System SI™ technology, or other compatible simulators such

as Spectre® and HSPICE.

Features

• Identifies the root cause of SI/PI issues and verifies fixes

• Improves accuracy of results in flows that use HSPICE and third-party simulators

• Verifies behavioral model accuracy versus the original transistor model with an

included time domain simulation wizard

• Accuracy checks are included as part of the model conversion process

• Highly automated and easy to use for those familiar with available IBIS model

formats

• All IBIS BIRD95/BIRD98 power-aware effects are included

• Streamlined flow for Sigrity SPEED2000 and SystemSI users

|