| |

Cloud-ready physical signoff solution

Key Benefits

• Flexible cloud-ready platform provides elastic and flexible compute environment

• Massively parallel architecture provides unprecedented speed and capacity

• Gigascale processing dramatically reduces full-chip physical verification runtimes

• Near-linear scalability across 100s of CPUs enables predictable runtimes

• Efficient use of CPU resources regardless of machine configuration and physical location

• Low transition cost using existing foundry-certified rule decks

• Native compatibility with Virtuoso® custom and the Innovus™ Implementation

System platforms

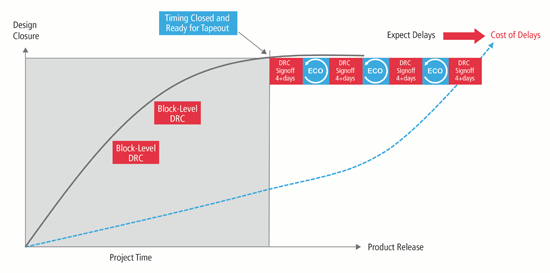

With the exponential increase in design rule check (DRC) complexity at advanced nodes, existing

DRC solutions haven’t been able to support the turnaround requirements needed to ensure design

schedules are met. Current DRC turnaround time takes several days using 64 CPUs, which is the

optimal configuration for existing tools. Adding more CPUs does not improve the turnaround time

because of the poor scalability of the current tools. At advanced nodes, DRC signoff cannot be run

overnight, and even breaking up the deck and running sub-decks in parallel cannot meet the overnight

runtime that critical projects need.

|

Current DRC turnaround time can take several days. Adding even more CPUs does not improve

the turnaround time because the tool scalability falls short |

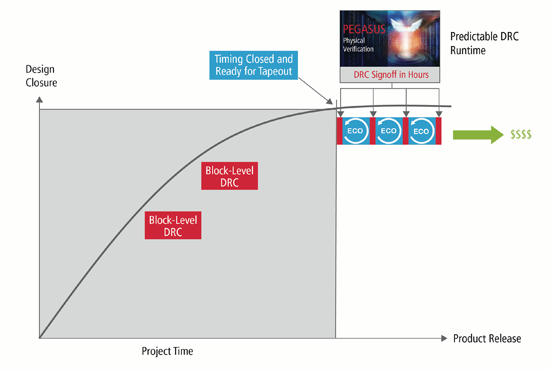

The Cadence® Pegasus® Verification System is a cloud-ready physical verification signoff solution,

which enables engineers to deliver advanced-node integrated circuits (ICs) to market faster. The

groundbreaking technology delivers up to 10X improved performance on DRC runs and reduces

turnaround time from days to hours. The Pegasus system’s innovative architecture and native cloud

processing provides an elastic and flexible computing environment. Customers can now achieve

complete full-chip signoff DRC on advanced-node designs in a matter of hours, helping designers

deliver products to market faster, or easily run multiple DRC signoff iterations, if needed, at the

time of tapeout.

|

Using the Pegasus system, jobs that previously ran for days can be completed in just a few hours,

and offer predictable DRC run times with near-linear scalability |

The Pegasus system provides a massively parallel architecture. It is the first solution to combine a

pipelined infrastructure with stream processing delivering near-linear scalability across 100s of CPUs.

The Pegasus system’s gigascale technology enables full-chip signoff DRC in just a few hours versus

days. As many designs continue to grow in complexity, the Pegasus system can scale to meet

customers’ stringent time-to-market requirements.

|