| |

Ensure reliable power delivery

Key Benefits

• Ensures reliable power delivery

• Lowers costs, reduces delays, and prevents field failures

• Provides conclusive IR drop analysis for package and board

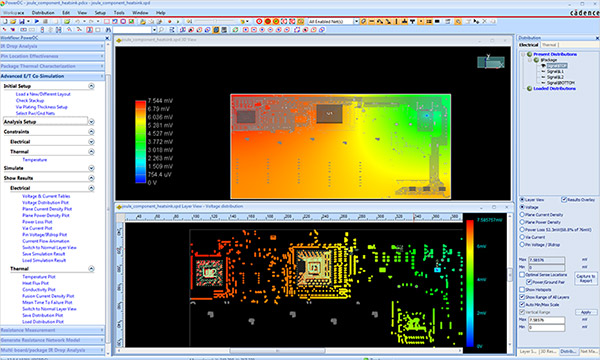

To ensure you achieve reliable power delivery, Cadence® Sigrity™ PowerDC™

technology provides efficient DC analysis for signoff of IC package and PCB designs,

including electrical/thermal co-simulation to maximize accuracy. PowerDC technology

quickly pinpoints excessive IR drop, along with areas of excess current density and

thermal hotspots to minimize your design’s risk of field failure.

DC analysis shows different layers of the PCB and the amount of voltage drop

across the board

Features

• Automatically set-up DC simulations using PowerTree™ data (source/sink

definitions) captured at the schematic stage of the design process

• Identifies difficult-to-locate highly resistive routing neck-downs and finds the one

via among thousands that will fail under stress

• Determines if it is possible to reduce plane layers without adding DC or thermal

reliability risk

• Assesses multi-structure PCB and package designs along with chip-level information

• Considers what-if improvement options with a unique block-diagram results view,

and a range of visualization options,

• Easy-to-deploy workflow that is ideal for occasional users and experts alike

• Patented automation to pinpoint the best remote sense line location

• Highly accurate, even for complex designs with multiple voltage domains and complex

plane structures

• Comprehensive support for multi-structure designs including stacked die, multiple

boards, and all popular package types

• Visualize the power portion of your schematics with PowerTree data

• Run pre-layout simulation without copper using PowerTree data to help select

components that meet design criteria

• Optimized for flows with Cadence SiP Layout, Allegro® Package Designer, and

Allegro PCB Designer

• Readily used in Mentor, Zuken, and Altium flows, accepting a mix of CAD databases

where needed for multi-structure design support

|