| |

Complete solution for analysis of source-synchronous parallel buses

Key Benefits

• Parallel bus analysis can begin early and continue through final signoff

• Enables large interconnect structures to be simulated

• Provides complete report data to compare against industry-standard

protocols

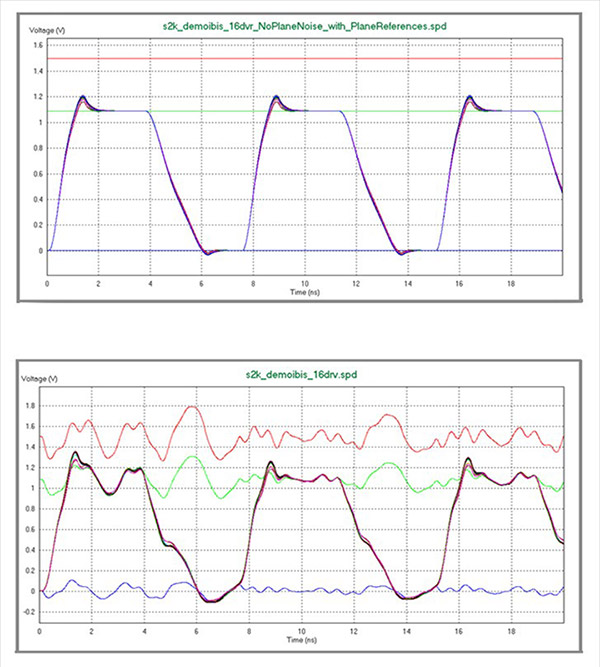

Simultaneous switching noise (SSN) can play havoc with your system’s timing, so the

Cadence® Allegro® Sigrity™ Power-Aware SI Option to the Allegro Sigrity SI Base

provides a complete solution for the analysis of the main causes of SSN, such as

source-synchronous parallel buses used for DDR3 and DDR4. The option comprises a

number of Sigrity tools that starts you with behavioral (IBIS 5.0+) model creation,

followed by interconnect extraction, and finally power-aware parallel bus analysis to

determine if your timing margins are being met.

Non-ideal power/ ground simulation (bottom) vs. ideal power / ground simulation (top)

The Allegro Sigrity Power-Aware SI Option lets you start parallel bus analysis early,

beginning with a virtual prototype of the full die-to-die topologies for the bus of interest.

This is created using a transmission line editor, a via creation tool, and IBIS 5.0

power-aware I/O models that accurately represent transistor-level buffer models, yet

simulate in a fraction of the time.

As the design progresses, pre-layout interconnect models can be replaced with more

detailed extracted models in a top-down methodology. Once transistor-level models are

updated for the I/Os, you can easily convert them to IBIS models, which in turn allows the

die-to-die simulation to proceed rapidly to ease system-level analysis of the detailed system.

With IBIS 5.0 behavioral models, you can accurately model simultaneous switching outputs

(SSOs) and see their effect on the stability of the power and ground rails. The effects on

timing will be seen in the report files generated. Another way you can speed up simulation

time is to utilize the S-parameter conversion utility to generate broadband SPICE

macromodels, which simulate faster, yet with equal accuracy.

|