| |

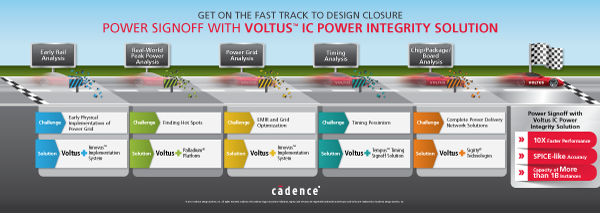

Rapid power signoff and design closure

Key Benefits

• Performs complete power integrity analysis up to 10X faster on designs with more

than a billion instances, with silicon-proven accuracy

• Can work standalone or in a highly integrated flow with Cadence digital design and

signoff products

• Supported by major foundries and IP providers

Cadence® Voltus™ IC Power Integrity Solution is a full-chip, cell-level power signoff tool that provides

accurate, fast, and high-capacity analysis and optimization technologies. The Voltus tool is of particular

value to designers for debugging, verifying, and fixing IC chip power consumption, IR drop, and

electromigration (EM) constraints and violations. Use the tool to:

• Calculate and analyze power consumption

• Analyze and optimize EM and IR-drop (EMIR)

• Analyze impact of power on design closure, from chip to package to PCB

The Voltus solution includes innovative technologies such as massively parallel execution, that can be

either multi-threaded or distributed-processing, and physically aware power grid analysis and

optimization. Beneficial as a standalone power signoff tool, Voltus IC Power Integrity Solution delivers

even more significant productivity gains when used in a highly integrated flow with other key Cadence

products, including Cadence Innovus™ Implementation System, providing the industry’s fastest design

closure technology. When used with Cadence Voltus-Fi Custom Power Integrity Solution, a transistor-

level electromigration and IR-drop (EMIR) tool delivering foundry-certified SPICE-level accuracy, the

resulting platform accelerates IC power signoff and overall design closure.

Supported by major foundries and intellectual property (IP) providers, Voltus IC Power Integrity Solution

has been validated and certified on advanced node processes such as 16nm/10nm/7nm FinFET and

28nm/22nm FDSOI and also included in reference design flows such as for 3D-IC technology.

Developed with advanced algorithms and a power integrity analysis engine with massively parallel

execution, the solution:

• Delivers power signoff accuracy via advanced algorithms in a SPICE-level matrix solver, accurate

signoff-quality power grid RC extraction, and accurate instance power distribution

• Supports designs with up to one billion instances with its hierarchical architecture

• Enhances physical implementation quality via physically aware power integrity optimization

• Provides early rail analysis at floorplanning and power planning to foster correct-by-construction

power grid design and remove correlation risks between implementation and signoff

• Provides automatic de-coupling capacitance analysis and optimization, as well as automatic power-

gating analysis and optimization

|

| Cadence - Voltus IC Power Integrity Solution |

|