| |

Multi-language simulation for testbench automation, metric-driven verification,

and mixed-signal verification

Key Benefits

• Fuels testbench automation, analysis, and reuse for increased productivity

• Ensures verification quality by tracking industry-standard coverage metrics

• Drives and guides verification with an automatically back-annotated and executable

verification plan

Whether you and your team are challenged by countless runs to meet closure and coverage goals,

interactive efforts to validate power domain and reset verification intent, or finding and debugging

long deep deadlocks, Incisive® Enterprise Simulator improves turnaround time and throughput.

With process automation technology, native high-performance engines, power analysis, and advanced

debug capabilities, you can verify the most complex chips and systems.

Incisive Enterprise Simulator supports all IEEE-standard languages and methodologies as well as power

formats and provides a comprehensive plan-to-closure methodology, improving productivity, project

predictability, and product quality. Its unique capabilities support the intent, abstraction, and

convergence needed to simplify and accelerate your workflow and help take the risk out of verification.

The simulator acts as the:

• Core engine for low-power verification working closely with Conformal® Low Power

• Digital engine for mixed-signal verification working with Virtuoso® simulators

• Testbench engine for simulation acceleration with the Palladium® platform

• RTL engine working with transaction-level modeling (TLM) verification solutions

When digital simulation became commonplace in the 1980s, flows were simple: RTL, then gate, then

implement. Since then, simulation has matured into verification and has become the critical means to

enable productivity, predictability, and quality in complex FPGAs, ASICs, and custom designs. As part of

that maturation, what has emerged are new means for generating metrics (to measure the progress

against the verification plan), new abstractions for both digital and analog simulation (to move verification

earlier in the process), and new methods for speeding convergence.

Incisive Enterprise Simulator is the most used engine in the industry, continually providing new technology

to support each of the verification niches that have emerged. Today, the simulator fuels testbench

automation, reuse, and analysis to verify designs from the system level, through RTL, to the gate level.

It supports the metric-driven approach implemented by Integrated Metric Center and the Cadence

vManager™ platform. Its native-compiled architecture speeds the simultaneous simulation of transaction-

level, behavioral, low-power, RTL, and gate-level models—critical to the verification of modern multi-

language, multi-abstraction, mixed-signal SoCs.

With Incisive Enterprise Simulator, you can gain a simplified overall debugging effort and shortened debug

turnaround time. The simulator separates design failures from simulation failures, sorting and grouping

these failures for easy selection and action. Its comprehensive language support enables source-code

debug for complex mixed-language SoCs, where it's critical to trace data through multiple blocks of IP to

identify and fix errors. Its integrated support for low-power, mixed-signal, and embedded software enables

debug for any SoC configuration.

Cadence provides integrated, sophisticated debug solutions to address all of your RTL, testbench, and SoC

verification debug needs:

• Indago™ Debug Platform: Highly integrated across the Incisive platform, the Indago Debug Platform

reduces debug time by 50% using automated root-cause analysis and patented predictive analysis

methods to take you directly to the cause of bugs across your SoC hierarchy, including your design

code, testbench, embedded software, and IP protocols.

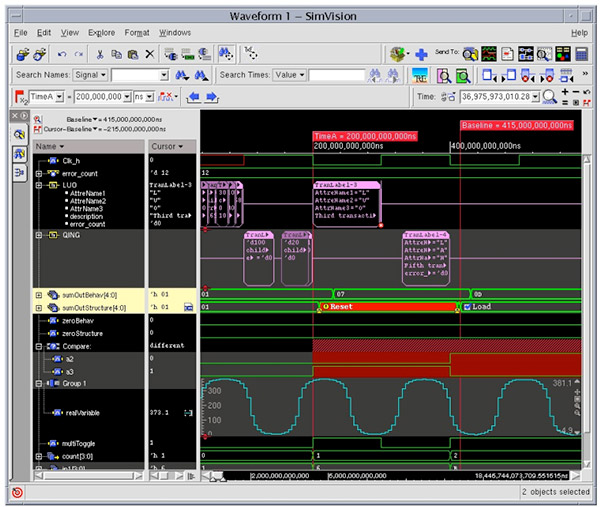

• SimVision™ Debug: A unified graphical debugging environment integrated with the Indago Debug

Platform, SimVision Debug supports signal-level and transaction-based flows across all IEEE-standard

design, testbench, and assertion languages, in addition to concurrent visualization of hardware,

software, and analog domains.

|

| Incisive Enterprise Simulator interface |

Incisive Enterprise Simulator supports all IEEE-standard languages, the Open Verification Methodology

(OVM), Accellera’s Universal Verification Methodology (UVM), and the e Reuse Methodology (eRM), making

it quick and easy to integrate with your established verification flows. You can extend the functionality of

the Incisive Enterprise Simulator with our Virtual System Platform, which provides a high-throughput

channel between the testbench and the device under test (DUT). This enables automated metric-driven

verification of embedded software exactly as if it were another part of the DUT.

Key Features

• Fuels testbench automation, analysis, and reuse for increased productivity

• Ensures verification quality by tracking industry-standard coverage metrics including functional,

transactional, low-power, and HDL code, plus automatic data and assertion checking

• Drives and guides verification with an automatically back-annotated and executable verification plan

• Creates reusable sequences and multi-channel virtual sequences on top of a multi-language verification

environment

• Configures existing Universal Verification Components (UVCs) or quickly constructs all-new UVCs

• Enables advanced debug using SimVision Debug for transaction-level models, SystemVerilog/e class

libraries, and transient mixed-signal, low-power, and traditional waveform analysis

• Supports e, Open Verification Library (OVL), OVM class library, UVM class library, SystemC®, SystemC

Verification Library, SystemVerilog, Verilog, VHDL, PSL, SVA, and CPF

• Delivers the highest possible performance across multiple levels of abstraction, supporting the ability to

“hot swap” the RTL simulation in/out of the Palladium XP accelerator/emulator

|