| |

Complete solution for analysis of multi-gigabit serial links

Key Benefits

• Accelerates time to design, lowers overall cost

• Enables bit error rate (BER) prediction

• Integrates with Cadence PCB and IC package layout editors and

Allegro Design Authoring

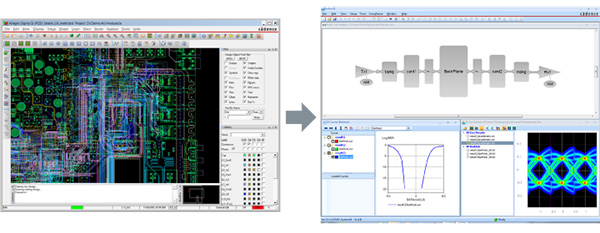

You can start using the Cadence® Allegro® Sigrity™ Serial Link Analysis Option at

the earliest stages of design, before schematic netlists and physical layouts are available.

For example, begin by performing feasibility studies with full die-to-die channel topologies

for the serial link of interest using a transmission line editor, a via creation tool, and

sample AMI models.

As the design progresses, you can replace pre-layout models with more detailed extracted

models in a top-down methodology. When IBIS-AMI models are not available, use a

wizard-based approach to choose equalization techniques to create representative models

(requires access to C compiler) for use in Cadence tools.

For interconnect modeling, you can use the tool’s accurate field solver engines to create

detailed post-layout S-parameter extraction of physical layout, and populate blocks in

the schematic simulation environment. If you’d like to accelerate simulation time and

enhance convergence, you can convert these S-parameters to SPICE sub-circuits.

Features

• Easy-to-use block-level schematic simulation environment

• High-capacity channel simulation

• Hybrid solver for efficient S-parameter extraction of large interconnect structures

• 3D full-wave solver for detailed extraction of high-frequency structures

• S-parameter tuning, checking, and Broadband SPICE® model conversion

• Electrical compliance checking against multi-gigabit standard specifications

• Enables a single user access to the following Sigrity products in either point tool mode

or as an integrated Allegro Sigrity solution:

• Sigrity Broadband SPICE

• Sigrity T2B

• Sigrity PowerSI

• Sigrity PowerSI 3D EM Extraction Option

• Sigrity SystemSI—Serial Link Analysis

|