| |

Concurrent die/package planning and route optimization

Key Benefits

• Optimizes device and system performance

• Significantly shortens time to converge on optimal die/package interface

• Anticipates and avoids downstream issues with early design planning

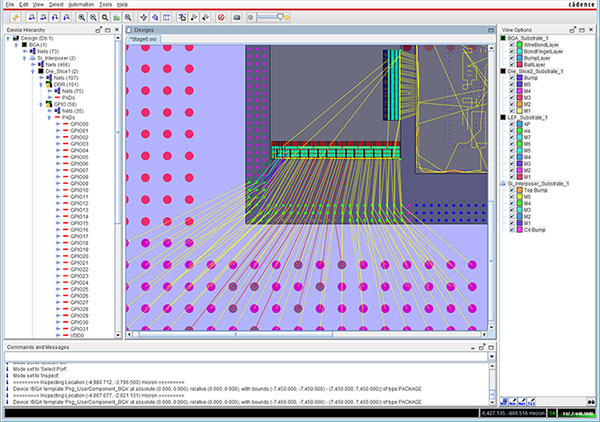

Cadence® OrbitIO™ Interconnect Designer helps your design team quickly assess

and plan connectivity between the die and package in context of the full

system—all within a single-canvas multi-fabric environment. It’s ideal for system

architects or anyone responsible for developing the die-to-package interface and

coming up with the optimal combination of bump/ball configurations and net

assignments. OrbitIO Interconnect Designer helps semiconductor companies evaluate

route feasibility of the package, as well as develop and communicate a route plan to

their package design resources.

Unlike an iterative spreadsheet-based approach, OrbitIO Interconnect Designer lets

you make or refine decisions, then immediately visualize and evaluate the impact on

adjacent fabrics, all within a single tool. In doing so, it significantly reduces iterations

between your silicon and package design teams as they try to converge on a solution.

OrbitIO interconnect designer helps you better qualify the design definition prior to

implementation, leading to more predictable system cost, performance, and product

delivery.

Features/Benefits

• Parametric definition and editing of bump and ball pad patterns

• Automatic ratio-driven signal, power, and ground pin allocation

• Pin-based floorplanning of critical nets and interfaces

• Automatic net mapping and propagation across fabrics, including differential pairs

• Route bundles and flow planning for detailed connection assignment

• Rapid route feasibility analysis to evaluate escape routes of bumps and balls

• Direct integration with Cadence SiP Layout XL (SIP-XL) to exchange planning

data and accelerate implementation

• Utilize key PCB components to influence package ball pad assignments

• Better predict cost and performance using well-qualified design definitions

• Quickly generate design abstractions in response to marketing feasibility studies

• Clearly communicate design intent and route plan to external design resources

• Design tool compatibility with outsourced assembly and test (OSAT) providers

|