| |

Features

★ High performance / small footprint DFI 3.1 compliant PHYs – DDR2, DDR3, DDR4, LPDDR2, LPDDR3, LPDDR4

★ Low power operation

★ Supports DDR3 at 2.133 Gbps / DDR4 at 2.4 Gbps

★ Built-in DSCL and DABC circuitry for highest performance, low power and field reliability

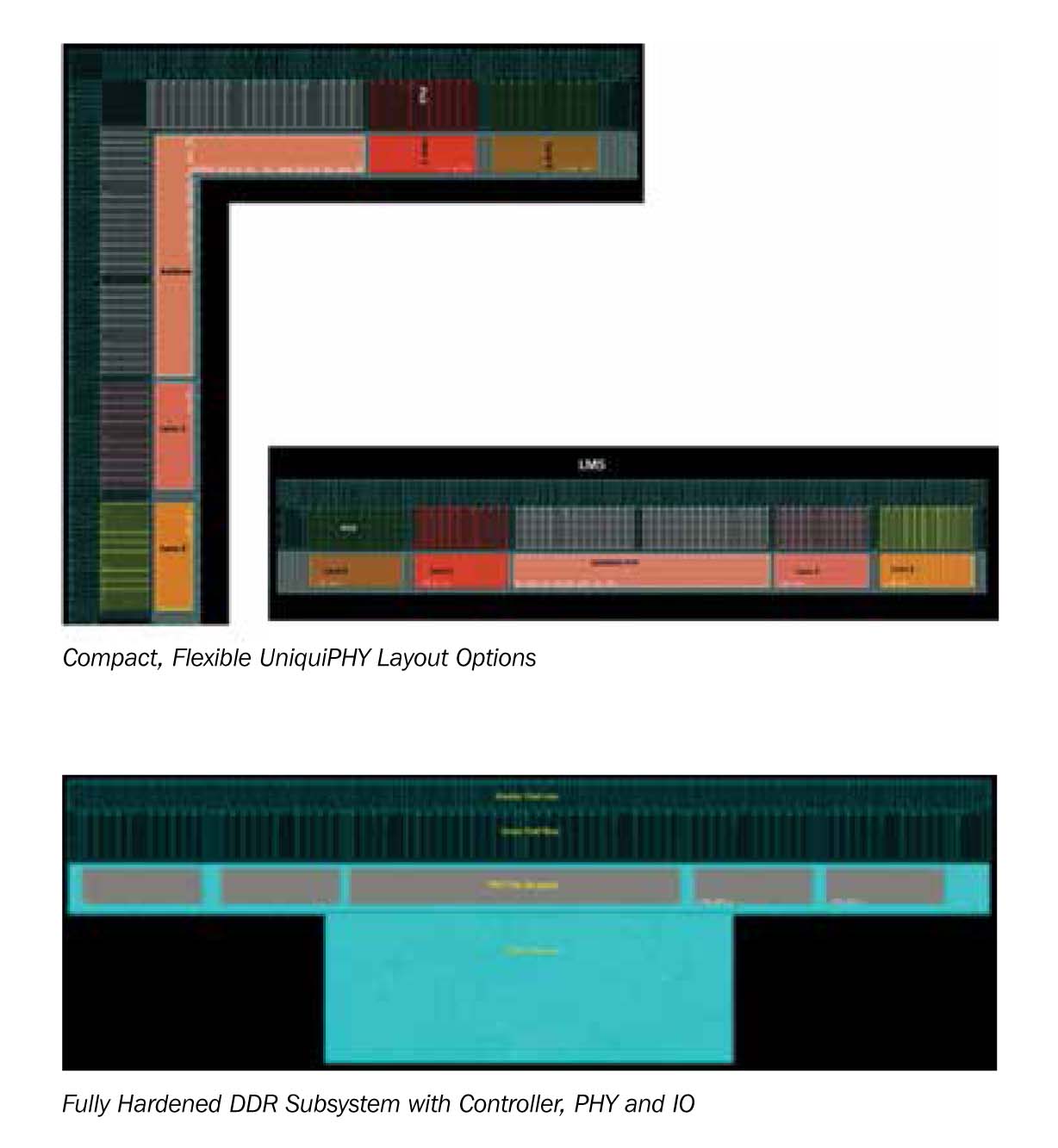

★ Flexible support — rectilinear layouts

★ Many options for Combo PHYs that support multiple DDR protocols such as LPDDR2/DDR3 and DDR3/DDR4

UniquiPHY™ — DFI Compatible PHY

UniquiPHY — leading edge DDR PHY IP innovated and designed by Uniquify and proven in production silicon. By combining a DFI 3.1 compatible PHY interface with patented self-calibrating logic (DSCL) and adaptive bit calibration (DABC) technologies, the UniquiPHY family offers the following key benefits:

★ Highest possible DDR performance

★ Smallest footprint available

★ Highly flexible, rectilinear PHY layouts

★ Lowest power

★ Lowest latency

★ Automated, fast DDR bringup

★ Best system reliability and improved yield

★ Simplified operation via register programming

★ DFI 3.1 compatibility with backward compatibility to earlier DFI standards for ease of integration with custom,

DFI-compliant DDR controllers

The UniquiPHY family offers PHY solutions for DDR2/3/4 and LPDDR2/3/4 with speeds up to 2.4Gbps and silicon-proven solutions at a wide variety of process nodes from 90nm through 28nm. Each PHY is delivered as a hardened block optimized to drop directly into the target SoC. When coupled with Uniquify's DDR IO IP, the combined solution eliminates tough timing problems such as data/clock skew, setup/hold time issues and complex physical implementation issues.

ONLY FROM UNIQUIFY:

SELF-CALIBRATING LOGIC TECHNOLOGY

The UniquiPHY family incorporates adaptive patented Self-Calibrating Logic (SCL) and Dynamic SCL (DSCL) technology that automatically calibrates the DDR interface at power up and dynamically during system operation by centering the capture point in the middle of the timing window. Field-proven, SCL/DSCL mitigates both static and dynamic variations resulting in optimal DDR performance, improved device and system yield and reduced system bring-up time. SCL/DSCL automatically solves the clock domain crossing problem and by eliminating much of the conventional overhead circuitry required for synchronization results in a smaller, more compact, lower power PHY. The operation of SCL/DSCL is completely user-controllable.

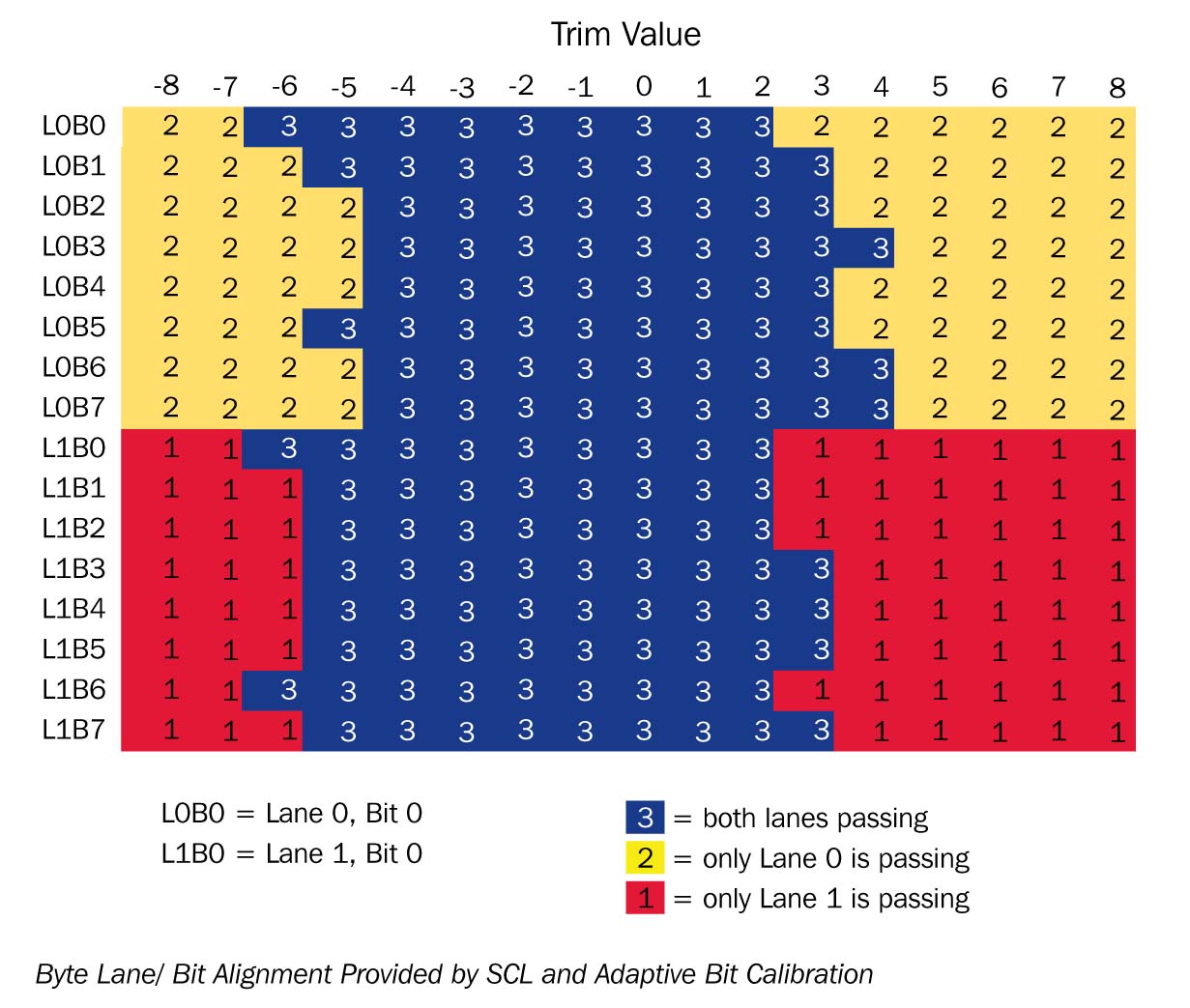

Read data capture timing and write alignment timing are setup automatically within the PHY at initialization using SCL

and DSCL is periodically re-run once every few seconds (or as specified by the user) in incremental calibration mode.

All setup and control of SCL and DSCL is accomplished using only register reads and writes and manual operation is also supported.

ADAPTIVE BIT CALIBRATION TECHNOLOGY

Uniquify's latest innovation is the addition of patented Adaptive Bit Calibration (ABC) and Dynamic ABC technology to the UniquiPHY family of DDR PHYs. Like SCL/DSCL, Adaptive Bit Calibration can be run both at system startup as well as dynamically during system operation.

ABC automatically corrects for bit-bit skew and jitter within each byte lane. This provides for a more robust system and allows optimal performance to be achieved for a given package/board/SDRAM.

Additional UniquiPHY Benefits

★ PHY hardened and delivered as GDS for ease of integration into host SoC

★ Flexible, rectilinear layout options minimize footprint

★ System bring-up time drastically reduced via SCL/DSCL technology

★ Patented Dynamic Adaptive Bit Calibration technology minimizes intra byte-lane skew for improved DDR system performance

★ Enhanced ATE testability via SCL/DSCL — traditional loopback testing also supported

★ Industry-leading low read data capture latency and command output latency

★ Supports DFI clock disable feature for power savings

★ SDRAM interface widths from 16-bits to 144-bits with flexible byte lane address lane configurations

|