| |

PLDA XpressLite2 PCI Express® endpoint with DMA is a high performance, fully configurable semiconductor soft IP engineered for PCI Express® interfacing with Xilinx FPGAs. The XpressLite2 PCI Express® supports both Gen1(2.5 GT/sec)and Gen2(5.0 GT/sec)speeds. We recommend our XpressLite2 endpoint controller IP for designs that require an easy to use yet high-performance and robust PCI Express® interfacing solution for Xilinx FPGAs.

What's unique about our IP?

‧ Reference designs to get you started and allow you to deploy your applications.

Check out our FPGA Design Kits section.

‧ Software Design Environment with device drivers, API, and example GUI applications with source code

‧ We offer professional services to quickly and reliably customize our IP to fit any specific requirement.

‧ Our IP customization GUI(Wizard)

‧ Free evaluation program that includes the same deliverables and technical support as the licensed IP.

‧ The IP comes with our industry acclaimed technical support provided by the IP team.

Supported Xilinx FPGA families and Configurations

‧ PCI Express® 2.0 in Gen2 mode(5.0 GT/sec)

□ Virtex-5 FXT, Virtex-5 TXT:x1, x4

□ Virtex-6:x1,x4 at PIPE level

‧ PCI Express® 2.0 in Gen1 mode(2.5 GT/sec)

□ Virtex 5 FXT/LXT/SXT/TXT, Virtex 4 FX:x1, x4, x8

□ Spartan 6:x1, x4

□ Virtex 6:x1,x4,x8 at PIPE level

□ Virtex 5 FXT/LXT/SXT/TXT, Virtex 4 FX/LX, Spartan-3, with external PCIe 1.1/1.0a PHY chips

◆ Genesys Logic GL9714:x4, x8(Virtex only)

◆ NXP PX1012A:x1

◆ PMC Sierra PM8358:x8(Virtex only)

◆ TI xIO1100:x1

IP Features and Deliverables

‧ PCI Express® IP core in synthesizable Verilog and VHDL RTL encrypted or clear source code

□ Compliant with the PCI Express® Base Specification, revision 2.0

◆ Backwards compatible to the PCI Express® Base Specification, revision 1.1

□ Supports Native and Legacy Endpoint

◆ x1, x4, x8

◆ 1 Virtual Channel(VC)

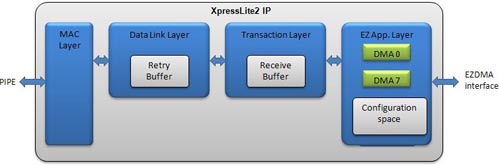

□ Includes Physical, Data Link, Transaction, and EZDMA Application layers

◆ Optimized for high throughput and minimal latency

□ PIPE interface to PHY

◆ 16-bit/125Mhz

◆ 8-bit/250Mhz

□ Maximum payload size up to 2KB

□ Number of outstanding read requests:up to 16

□ Up to 6 BARs plus expansion ROM

□ Full Power Management

□ DMA-based user's interface(EZDMA)

◆ Up to 8 DMA channels

◆ Scatter-Gather support with host based descriptors

◆ Integrated DMA arbitration optimized for maximum throughput

‧ PCI Express® Testbench simulation libraries

□ For Cadence NC-Sim, Mentor Modelsim, Synopsys VCS

‧ PCI Express® IP core simulation models

□ For Cadence NC-Sim, Mentor Modelsim, Synopsys VCS

‧ PIPE wrappers and Physical Coding Sub-layers(PCS)

□ For the supported Xilinx FPGA families with embedded PCI Express® transceivers

□ For the supported external PCI Express® PHY chips

‧ Configuration assistant GUI(Wizard)

□ Multi-platform JAVA based

‧ Endpoint reference design

□ Synthesizable Verilog and VHDL RTL source code

□ Simulation environments and scripts

□ FPGA synthesis/PAR environments and scripts

‧ Software Design Environment

□ 32-bit/64-bit Linux, 32-bit Windows XP PCI Express® device driver binary

◆ Source code availableas an option

□ C source code API

□ PCI Express® GUI tools and source code(C++, Java)

‧ Complete documentation

|