Highlights:

• Supports the PCIe® 6.0 specification, including 64GT/s data rates,

FLIT mode, and L0p power state.

• Designed for configurability to satisfy a multitude of customer and

industry use cases.

• A proven leader in PCIe controller design, PLDA IP ensures our

customers high performance, ease-of-integration and first-pass

silicon success.

PLDA, the leading developer of high-speed interconnect silicon IP, today

announced the launch of their XpressRICH™ PCI Express® (PCIe®)

Controller IP for the PCIe 6.0 specification. The PCIe 6.0 specification

provides an evolutionary step forward by doubling the data rate to 64

GT/s link rate negotiation. PCIe 6.0 architecture will be essential for SoC

designers and system architects creating next generation chips that require

the movement of large amounts of data within systems, in applications

including:

• HPC/Cloud Computing

• AI and Machine Learning

• Enterprise Storage

• Enterprise Networking

• Automotive

To support configurability for XpressRICH users, PLDA has implemented

a large number of features and ECN that can be fully parameterized

through the included configuration assistant.

Read The Full Article

|

|

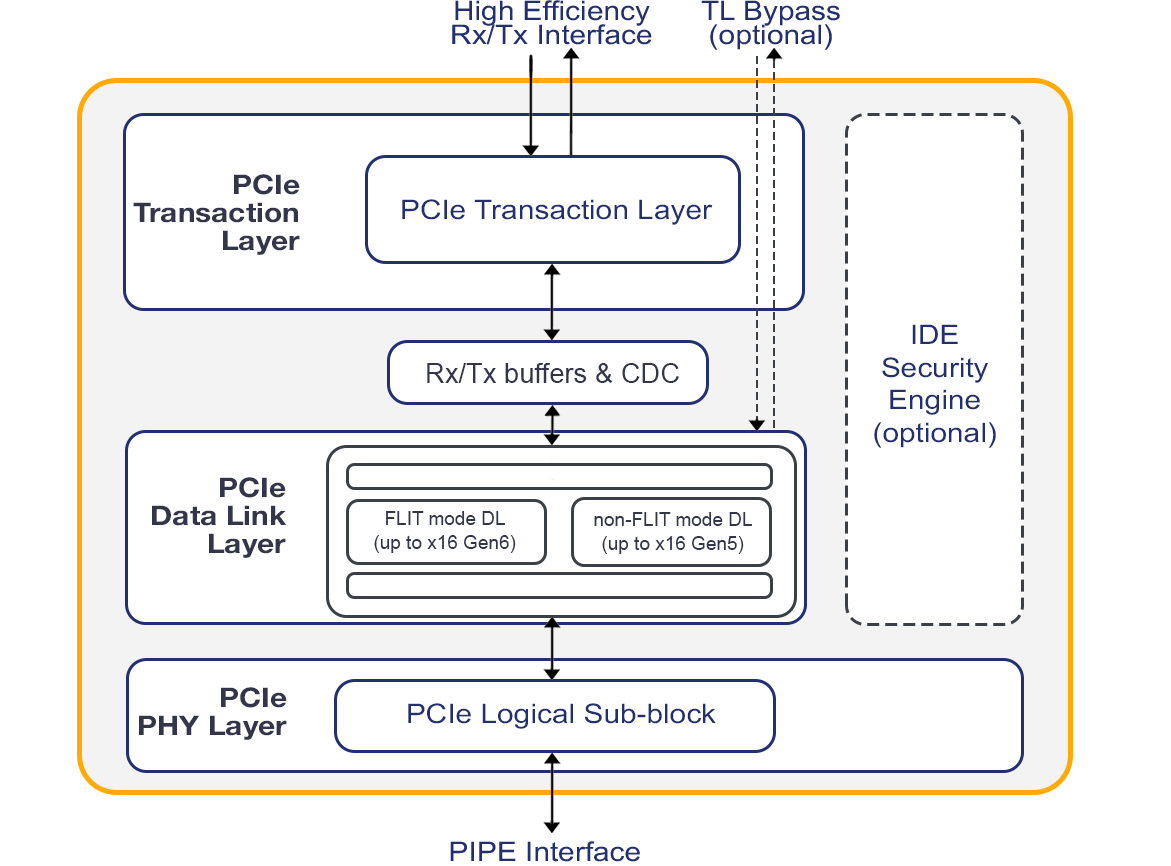

XpressRICH for PCIe 6.0

Controller IP for PCIe 6.0, Supporting Root

Port, Endpoint, Dual-mode, Switch Port

Configurations with Native User Interface

XpressRICH for PCIe 6.0 Product Page

|

|

|

Webinar

In this webinar, we present the main

characteristics of the PCIe 6.0 protocol in

contrast to earlier revisions, and explain the

rationale behind the main architecture changes.

We then take a look at PCIe 6.0 from the

perspective of silicon IP enablement, by

introducing the main design features required

to take full advantage of the new level of

performance offered by PCIe 6.0.

|

Blog Article

With the announcement of PLDA's PCIe 6.0

controller IP, Paul Karazuba, VP Marketing

at PLDA, initiates today the first chapter of

a blog series dedicated to the PCIe 6.0

specification.He reminds us of the history

of PCIe and explains to us the differences

between this latest PCIe generation and

the previous ones.

|

|

|

Copyright© 2021 PLDA, All rights reserved.

|