Highlights:

• Optimized integration of PLDA CXL 2.0 controller and AnalogX

ultra low power PHY reduces latency by over 50% and power

by 40% compared to leading competitive solutions

• Improves system performance at no extra cost, while

pre-configured integration reduces design time and speeds

time-to-market

PLDA, the leading developer of high-speed interconnect silicon IP, and

AnalogX, the leading provider of low power multi-standard connectivity

SerDes IP solutions, today announced an optimized integration of PLDA

CXL™ 2.0 controller and AnalogX 32G-MR PHY that reduces latency by

50% and power consumption by 40% compared to leading competitive

solutions.

The CXL (Compute Express Link™) standard was developed to scale

heterogeneous computing in the data center and provide more efficient

data movement for compute-intensive workloads, specifically where

latency requirements were not met by existing interface standards.

Read The Full Article

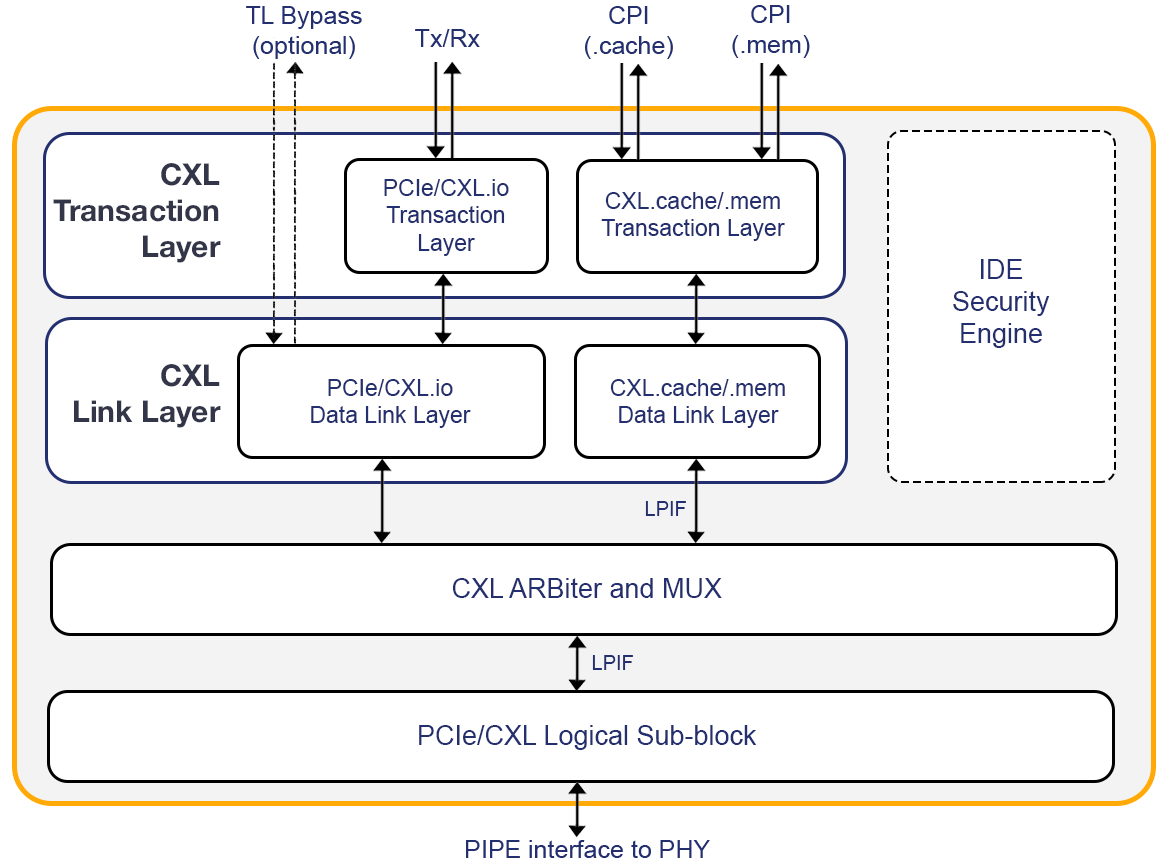

XpressLINK Controller IP for CXL 2.0

Controller IP for the Compute Express Link (CXL) Specification supporting CXL.io,

CXL.cache, CXL.mem

XpressLINK™ is a parameterizable Compute Express Link (CXL) controller Soft IP designed

for ASIC and FPGA implementation. The XpressLINK Controller IP leverages PLDA's silicon

proven XpressRICH Controller for PCIe 5.0 architecture for the CXL.io path, and adds the

CXL.cache and CXL.mem paths specific to CXL.

Visit the Product Page

Copyright© 2021 PLDA, All rights reserved.

|