____________________________________________________________________________

|

Winter Newsletter 2024 |

____________________________________________________________________________

More, more, more…Gen AI and other advanced workloads keep upping the demands for

greater bandwidth, greater capacity and greater reliability.

In server main memory, the rapid rate of evolution means we're already progressing to the

5th generation(!) of DDR5 memory running at 8000 MT/s. Our newly announced Gen 5 DDR5

Registering Clock Driver (RCD) will be a key enabler of RDIMM 8000s.

And of course we can't stop there. Multiplexing two data streams effectively doubles the

bandwidth a memory module can provide, enabling the memory bus to operate at twice the

native data rate of the memory devices. MRDIMM 12800 will operate at 12,800 MT/s using

DDR5 6400 DRAM.

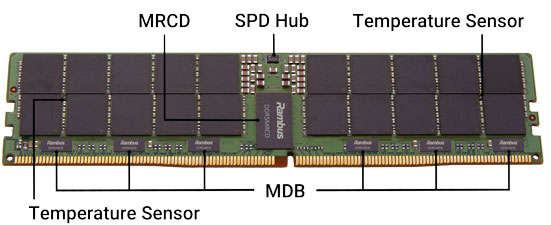

Making that multiplexing magic happen requires two new chips that we've introduced: a

Multiplexing Registering Clock Driver (MRCD) and a Multiplexing Data Buffer (MDB). Each

MRDIMM 12800 will use one MRCD and ten MDB to mux and demux the data stream and

steer it to and from the correct DRAM device.

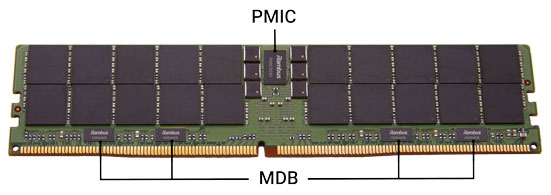

Given the greater chip content and higher power requirements, we've introduced a new power

management IC – the PMIC 5030 – to comfortably handle the power requirements of

MRDIMM 12800. In addition, all RDIMMs at 8000 MT/s and above will also use the PMIC 5030

as the standard power management solution.

______________________________________________________________________________

MEMORY INTERFACE CHIPS

Rambus Unveils Industry-First Complete Chipsets for

Next-Generation DDR5 MRDIMMs and RDIMMs to Deliver

Breakthrough Performance for Data Center and AI

DDR5 MRDIMM 12800 (front and back images) showingRambus MRDIMM

chipset

Two new chipsets for DDR5 MRDIMM 12800 and RDIMM 8000 enable state-of-the-art

memory bandwidth and capacity for next-generation servers tackling the most demanding

workloads.

You might also want to check out our latest episode of our Ask the Experts Series, where

we discuss DDR5 MRDIMMs.

________________________________________________________________________________

INTERFACE IP

Rambus Announces Industry-First HBM4 Controller IP to

Accelerate Next-Generation AI Workloads

Built on a proven track record of over one hundred HBM design wins, we’ve introduced the

industry’s first HBM4 Controller IP which can deliver more than double the throughput of

HBM3 to meet the demands of Gen AI and HPC.

________________________________________________________________________________

SECURITY IP

Root of Trust and Secure Authentication Solutions with

Tamper-Resistant PUF Technology

In this webinar available on-demand, Scott Best and BongHo Kang discuss how Rambus Root of

Trust and Secure Authentication solutions combined with ICTK’s PUF technology can provide a

highly robust hardware foundation to protect data, devices, and cloud.

Check out Rambus in the news:

Semiconductor Digest: Rambus Unveils Industry-First Complete Chipsets for Next-Generation

DDR5 MRDIMMs and RDIMMs

Forbes: Addressing AI's Insatiable Demand For Power

Wccftech: Rambus Outlines HBM4 Memory Controller: Up To 10 Gb/s Speeds, 2.56 TB/s

Bandwidth & 64 GB Capacities Per Stack

The Ojo-Yoshida Report: Will Quantum Computing Eliminate Privacy?

Fierce Electronics: GenAI adds the need for hardware-based security

Copyright © 2024, All rights reserved.

|