| |

The A2DPENC-SO1 and A2DPDEC-SO1 ASIC cores are designed to support Bluetooth A2DP mandatory SBC encoding/decoding for the ultra low power applications.

The A2DPENC-SO1 and A2DPDEC-SO1 codec can provide superior 16/32/44.1/48 KHz stereo audio compress/decompress power in real time with as little as 4 MHz operation clock. It can be used not only in the Bluetooth audio applications, but also in a wide range of audio/voice applications.

1. Important Features

‧ All A2DP decoding functions implemented at RTL level

‧ Gate count 22 K gates plus 1728 bytes data RAM

‧ Lowest power consumption(clock required 4 MHz)

‧ Single clock synchronous design

‧ Support Bluetooth A2DP SBC mono/dual/stereo/joint stereo audio decoding in 16/32/44.1/48 KHz

‧ Straightforward interfaces for SoC applications

‧ Fully synthesizable technology independent of verilog RTL code

2. Function Overview

A2DPDEC-SO1 takes SBC bitstream, automatically decompress it to 16 bits PCM audio format.

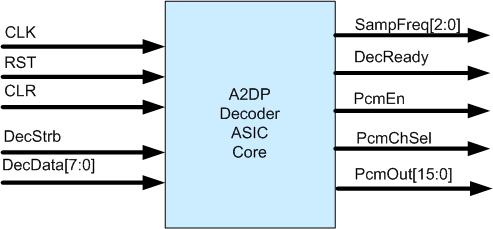

3. A2DPDEC-SO1 top level interface

Deliverables

‧ Synthesizable verilog source code

‧ Verilog testbench

|