|

Power integrity analysis for both the non-expert and the expert

Key Benefits

• Locates areas needing layout changes to improve power integrity

• Provides advanced modeling and PI simulation for PDN analysis

• Simulates PDNs at package or board level

• PFE aids in decoupling capacitor selection and placement

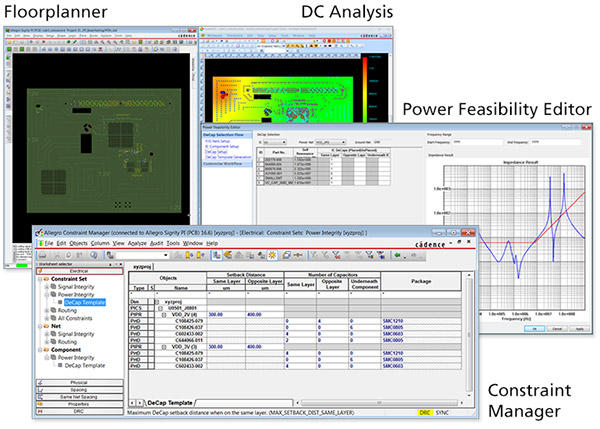

The Cadence® Allegro® Sigrity™ PI Base is an interactive design and analysis

environment with Allegro DRC markers locating areas that need layout changes to

improve power integrity (PI). In addition, advanced modeling and PI simulation is

provided in support of Power Delivery Network (PDN) analysis of high-speed and/or

high-current designs. The Allegro Sigrity PI Base simulates PDNs at the package or

board level.

Users of the Allegro Sigrity PI Base

technology can perform DC analysis

using the Sigrity PowerDC engine

without having to perform any manual

data translation. Set-up is automated

so that the default analysis settings

are always in place for the user. The

integrated solution for layout and

analysis can be used throughout the

design process. User-friendly guidance

is offered to assist the layout team on

how best to optimize the PDN.

Also included with the Allegro Sigrity PI

Base is a power feasibility editor (PFE) to

aid in decoupling capacitor selection and

placement. The Allegro constraint manager

is enabled with Power Integrity Constraint

Sets (PICsets) that can be reused from

design to design. When used during the

component placement phase of PCB or IC

package design, the PICset shows the layout

designer where to place the decoupling

capacitors so they will be most effective. |

Allegro technology works together with Sigrity

power integrity analysis technology

|

Integration of Allegro Sigrity PI Base and Allegro PCB Editor

Integrated with Allegro PCB and IC package design, editing, and routing technologies,

the Allegro Sigrity PI Base provides advanced PI analysis both during and post-layout.

As power and ground planes are designed and carved up to allow for signal routing and

vias, the analysis engine can be invoked to determine if DC IR drop is still within

specification.

The Allegro Sigrity PI Base reads and writes directly to the Allegro PCB and IC package

design database for fast and accurate analysis and viewing of results. Layout designers

can find first-order power integrity problems as they design. More advanced PI experts

also can use this technology for quick results, but will likely defer to the advanced technology

that is represented in Allegro Sigrity PI Signoff and Optimization Option for electrical-thermal

co-simulation and decoupling capacitor optimization.

Features

• Performs first-order PI analysis

• Early detection of design errors to increase likelihood of first-pass success

• Utilizes new PI-focused constraints to accelerate the design cycle time

• Tight integration between the design canvas and layout-focused analysis

• Points to physical locations where changes are required to improve PDN performance

|